#### **Public Products List**

Publict Products are off the shelf products. They are not dedicated to specific customers, they are available through ST Sales team, or Distributors, and visible on ST.com

**PCN Title :** New assembly and test line qualification for Rectifiers STTHxxDJF-TR and STPSxxDJF-TR housed in PowerFLATTM 5x6 package

PCN Reference : ADG/22/13659

Subject : Public Products List

Dear Customer,

Please find below the Standard Public Products List impacted by the change.

| STTH8R03DJF-TR  | STTH5R06DJF-TR   | STPS15L30CDJFTR |

|-----------------|------------------|-----------------|

| STTH30R02DJF-TR | STPS30H100DJF-TR | STPS30M60DJF-TR |

| STPS30L30DJF-TR |                  |                 |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

# PCN

# **Product/Process Change Notification**

# New assembly and test line qualification for Rectifiers STTHxxDJF-TR and STPSxxDJF-TR housed in PowerFLAT<sup>™</sup> 5x6 package

| Notification number:                  | ADG/22/13659    | Issue Date                                                                                                                       | 20-Sept-2022 |

|---------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|

| Issued by                             | Sophie da Silva |                                                                                                                                  |              |

| Product series affected by the change |                 | STTH30R02DJF-TR<br>STTH5R06DJF-TR<br>STTH8R03DJF-TR<br>STPS15L30CDJFTR<br>STPS30H100DJF-TR<br>STPS30L30DJF-TR<br>STPS30M60DJF-TR |              |

| Type of change                        |                 | Back-End realization                                                                                                             |              |

#### Description of the change

Qualification of a back-end subcontractor located in China (location B) for the assembly and test and finishing of Rectifiers products in PowerFLAT<sup>™</sup> 5x6.

The production currently located ST Shenzhen in China (location A) will be extended with subcontractor in China (location B) for Rectifiers products in PowerFLAT<sup>™</sup> 5x6.

This subcontractor in China (Location B) is already a major production site for ST products (FERD, Power Schottky and Ultrafast diodes technologies), including PowerFLAT<sup>™</sup> 5x6 package (with slight difference of package drawing compared to location A).

#### Reason for change

STMicroelectronics investment on Rectifiers production capacity increase.

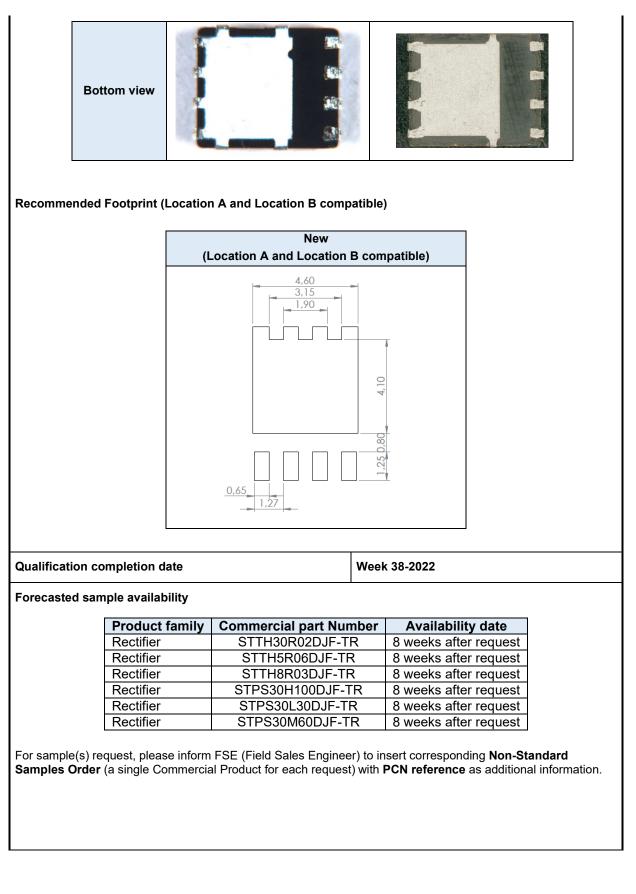

| Former versus changed product: | The changed products do not present modified electrical or thermal parameters.                                |

|--------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                | New recommended footprint (both locations compatible).<br>Refer to next page.                                 |

|                                | The Moisture Sensitivity Level of the part (according to the IPC/JEDEC JSTD-020D standard) remains unchanged. |

|                                | There is no change in the packing modes and the standard delivery quantities either.                          |

|                                | The products remain in full compliance with the ST ECOPACK®2 grade (so called "halogen-free").                |

(1) ADG: Automotive and Discrete Group

#### Marking and traceability

The product code marking is the same between plant A and B. Traceability of the BE plant will be ensured by an internal codification (Finished Good) and by the trace code (printed on device top side and on the carton box label). The first two digits of the trace code indicate the back-end plant origin.

| Commercial part number/Order<br>code | Current Finished<br>Good/Type | New Finished<br>Good/Type | Product code<br>marking |

|--------------------------------------|-------------------------------|---------------------------|-------------------------|

| STTH30R02DJF-TR                      | STTH30R02DJFR6/7              | STTH30R02DJFR/B           | TH30 R02                |

| STTH30R02DJF-TR                      | TH30R02DJFTR\$7               | TH30R02DJFTR\$B           | TH30 R02                |

| STTH5R06DJF-TR                       | STTH5R06DJFR6/7               | STTH5R06DJFR/B            | TH5R 06                 |

| STTH8R03DJF-TR                       | STTH8R03DJFR6/7               | STTH8R03DJFR/B            | TH8R 03                 |

| STPS15L30CDJFTR                      | PS15L30CDJFR6%7               | PS15L30CDJFRH%B           | PS15L 30C               |

| STPS30H100DJF-TR                     | PS30H100DJFR6%7               | PS30H100DJFTR%B           | PS30H 100               |

| STPS30L30DJF-TR                      | PS30L30DJFR6%7                | PS30L30DJFTR%B            | PS30 L30                |

| STPS30M60DJF-TR                      | PS30M60DJFR6%7                | PS30M60DJFTR%B            | PS30 M60                |

| Current Label<br>(Example for other Rectifier product)                                                                                                                                                                                                                                                                                                                 | New Label<br>(Example for other Rectifier product)                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FG ending by 7                                                                                                                                                                                                                                                                                                                                                         | FG ending by B                                                                                                                                                                                                                                                                                                                                 |

| Hanufactured under patents or patents pendins<br>Resembled in: CHINA<br>Pb-free 2nd Level Interconnect<br>MSL: I Not moisture sensitive<br>PBT: 280 C Tategory: 8 2COPHCK2ROHS<br>TYPE: FERDISSSODJF-TR<br>FERDISSSODJFTR/7<br>Total Qty: 120<br>Trace code GK80322C V5 GK<br>Monthing FDIS 550<br>Duilk 20 T8005JSXL190<br>Compared FDIS 550<br>Duilk 20 T8005JSXL190 | Hanufactured under patents or patents pending<br>Resembled in: CHINA<br>Pb-free 2nd Level Interconnect<br>MSL: I Not moisture sensitive<br>PBT: 260 C Eateory: e3 ECOPACK/2004<br>TYPE: FERDI5S50DJF/B<br>Total Qty: 3000<br>Trace code FPISESE US F<br>Marking FDIS 550<br>Bulk ID 88617DCZ0001<br>Fleese provide the bulk ID for any inquiry |

|          | Current<br>(Location A)                     | New<br>(Location B)                              |

|----------|---------------------------------------------|--------------------------------------------------|

| Top view | • 477 @ G<br>FD15 ()<br>S50 ()<br>GKO9N 252 | • 477 @ G<br>F D 2 D<br>U 5 D<br>G F 3 4 8 8 0 6 |

#### STMicroelectronics ADG<sup>1</sup> – Discrete and Filter Division

(1) ADG: Automotive and Discrete Group

(1) ADG: Automotive and Discrete Group

| Change implementation schedule                                                                                         |                      |          |                           |  |

|------------------------------------------------------------------------------------------------------------------------|----------------------|----------|---------------------------|--|

| Sales-types                                                                                                            | Estimated production | on start | Estimated first shipments |  |

| STTH30R02DJF-TR<br>STTH5R06DJF-TR<br>STTH8R03DJF-TR<br>STPS30H100DJF-TR<br>STPS30L30DJF-TR<br>STPS30M60DJF-TR          |                      |          | Week 47-2022              |  |

| Comments:                                                                                                              |                      |          |                           |  |

| Customer's feedback                                                                                                    |                      |          |                           |  |

| Please contact your local ST sales representative or quality contact for requests concerning this change notification. |                      |          |                           |  |

| Absence of acknowledgement of this PCN within 30 days of receipt will constitute acceptance of the change              |                      |          |                           |  |

| Absence of additional response within 90 days of receipt of this PCN will constitute acceptance of the change          |                      |          |                           |  |

| Qualification program and results 19015QRP rev.3 Attached                                                              |                      |          | rev.3 Attached            |  |

# Reliability Evaluation Report Qualification of PowerFLAT<sup>™</sup> 6x5 at Subcontractor in China

|                                                                     | General Information                                                                                                                                                                                                      | Locations                         |                                                     |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------|

| Product Line                                                        | Rectifiers                                                                                                                                                                                                               | Wafer fab                         | ST CATANIA – ITALY<br>ST SINGAPORE                  |

| Product Description                                                 | Field Effect, Power Schottky and<br>Ultrafast Rectifiers                                                                                                                                                                 |                                   |                                                     |

| Product perimeter                                                   | FERD15S50DFJ-TR, FERD20U50DJF-TR<br>FERD30M100DJF-TR, STPS3045DJF-TR<br>STPS30M100DJF-TR, STPS30120DJF-TR<br>STPS30170DJF-TR, STPS15L30CDJFTR,<br>STPS30H100DJF-TR, STPS30L30DJF-TR,<br>STPS30M60DJF-TR, STTH30R02DJF-TR | Assembly plant<br>Reliability Lab | SUBCONTRACTOR –CHINA<br>(998G)<br>ST TOURS - FRANCE |

| Product Group<br>Product division<br>Package<br>Maturity level step | STTH5R06DJF-TR, STTH8R03DJF-TR<br>ADG<br>Discrete and Filter Division<br>PowerFLAT <sup>™</sup> 5x6<br>Qualified                                                                                                         | Reliability assessment            | Pass                                                |

#### **DOCUMENT INFORMATION**

| Version | Date         | Pages | Prepared by     | Approved by                                                                                 | Comments                                                                                                                                                                                           |

|---------|--------------|-------|-----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 04-Dec-2018  |       |                 |                                                                                             | FERDxxx qualification:<br>FERD15S50DFJ-TR / FERD20U50DJF-TR<br>FERD30M100DJF-TR                                                                                                                    |

| 2.0     | 29-Jan-2019  |       | Isabelle BALLON | Julien MICHELON                                                                             | Power Schottky qualification:<br>STPS3045DJF-TR / STPS30M100DJF-TR<br>STPS30120DJF-TR / STPS30170DJF-TR                                                                                            |

| 3.0     | 07-Sept-2022 | 7     | Christophe GOIN | Julien Digitally signed<br>by Julien Michelon<br>Date:<br>2022.09.07<br>0N 10:52:05 +02'00' | Additional Power Schottky and Ultrafast rectifiers<br>qualification: STPS30H100DJF-TR<br>STPS30L30DJF-TR / STPS30M60DJF-TR<br>STPS15L30CDJFTR / STTH30R02DJF-TR<br>STTH5R06DJF-TR / STTH8R03DJF-TR |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

#### TABLE OF CONTENTS

| 1 |       | CABLE AND REFERENCE DOCUMENTS | - |

|---|-------|-------------------------------|---|

|   |       | BILITY EVALUATION OVERVIEW    | - |

| 5 |       |                               |   |

|   | 3.1   | Objectives                    |   |

|   | 3.2   | Conclusion                    |   |

| 4 | DEVIC | CE CHARACTERISTICS            | 5 |

|   | 4.1   | DEVICE DESCRIPTION            | 5 |

|   | 4.2   | Construction Note             | 5 |

| 5 | TESTS | RESULTS SUMMARY               | 6 |

|   | 5.1   | Test vehicle                  | - |

|   | 5.2   | TEST PLAN AND RESULTS SUMMARY |   |

| 6 | ANNE  | XES                           |   |

|   | 6.1   | TESTS DESCRIPTION             | 7 |

### **<u>1</u>** APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                                         |  |

|--------------------|---------------------------------------------------------------------------|--|

| JESD 47            | Stress-Test-Driven Qualification of Integrated Circuits                   |  |

| JESD 94            | Application specific qualification using knowledge based test methodology |  |

| JESD 22            | Reliability test methods for packaged devices                             |  |

## 2 GLOSSARY

| SS    | Sample Size                             |

|-------|-----------------------------------------|

| HTRB  | High Temperature Reverse Bias           |

| тнв   | Temperature Humidity Bias               |

| тс    | Temperature Cycling                     |

| UHAST | Unbiased Highly Accelerated Stress Test |

| RSH   | Resistance to Soldering Heat            |

| SD    | Solderability                           |

| DBT   | Dead Bug Test                           |

| GD    | Generic Data                            |

| PC    | Pre-conditioning (before test)          |

#### 3 RELIABILITY EVALUATION OVERVIEW

#### 3.1 **Objectives**

The objective of this report is to qualify PowerFLAT<sup>™</sup> 5x6 at subcontractor in China (998G).

The involved products are listed in table here below:

| Commercial Product |

|--------------------|

| FERD15S50DFJ-TR    |

| FERD20U50DJF-TR    |

| FERD30M100DJF-TR   |

| STPS3045DJF-TR     |

| STPS30M100DJF-TR   |

| STPS30120DJF-TR    |

| STPS30170DJF-TR    |

| STPS15L30CDJFTR    |

| STPS30H100DJF-TR   |

| STPS30L30DJF-TR    |

| STPS30M60DJF-TR    |

| STTH30R02DJF-TR    |

| STTH5R06DJF-TR     |

| STTH8R03DJF-TR     |

The reliability test methodology used follows the JESD47-H: « Stress Test Driven Qualification Methodology ». The following reliability tests ensuing are:

- TC to ensure the mechanical robustness of the products.

- HTRB to evaluate the risk of contamination from the resin and the assembly process versus the die layout sensitivity.

- THB, UHAST to check the robustness to corrosion and the good package hermeticity.

- RSH, Solderability and DBT to check compatibility of package with customer assembly.

#### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. Reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the robustness of the products and safe operation, which is consequently expected during their lifetime.

### **<u>4</u> DEVICE CHARACTERISTICS**

#### 4.1 **Device description**

Refer to products datasheets.

### 4.2 Construction Note

|                                           | FERD15S50DJF / FERD20U50DJF / FERD30SM100DJF |

|-------------------------------------------|----------------------------------------------|

| Wafer/Die fab. information                |                                              |

| Wafer fab manufacturing location          | ST Catania (ITALY)                           |

| Technology / Process family               | Field Effect Rectifier                       |

| Wafer Testing (EWS) information           |                                              |

| Electrical testing manufacturing location | ST SINGAPORE                                 |

| Assembly information                      |                                              |

| Assembly site                             | Subcontractor in CHINA (998G)                |

| Package description                       | PowerFLAT <sup>™</sup> 5x6                   |

| Molding compound                          | ECOPACK <sup>®</sup> 2 compliant component   |

| Lead finishing/bump solder material       | Pure Tin                                     |

| Final testing information                 |                                              |

| Testing location                          | Subcontractor in CHINA (998G)                |

|                                           | STPS3045DJF-TR / STPS30M100DJF-TR / STPS30120DJF-TR / STPS30170DJF-TR<br>STPS15L30CDJFTR / STPS30H100DJF-TR / STPS30L30DJF-TR / STPS30M60DJF-TR |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Wafer/Die fab. information                |                                                                                                                                                 |

| Wafer fab manufacturing location          | ST SINGAPORE                                                                                                                                    |

| Technology / Process family               | Power Schottky                                                                                                                                  |

| Wafer Testing (EWS) information           |                                                                                                                                                 |

| Electrical testing manufacturing location | ST SINGAPORE                                                                                                                                    |

| Assembly information                      |                                                                                                                                                 |

| Assembly site                             | Subcontractor in CHINA (998G)                                                                                                                   |

| Package description                       | PowerFLAT <sup>™</sup> 5x6                                                                                                                      |

| Molding compound                          | ECOPACK <sup>®</sup> 2 compliant component                                                                                                      |

| Lead finishing/bump solder material       | Pure Tin                                                                                                                                        |

| Final testing information                 |                                                                                                                                                 |

| Testing location                          | Subcontractor in CHINA (998G)                                                                                                                   |

|                                           | STTH30R02DJF-TR / STTH5R06DJF-TR / STTH8R03DJF-TR |

|-------------------------------------------|---------------------------------------------------|

| Wafer/Die fab. information                |                                                   |

| Wafer fab manufacturing location          | ST Tours (FRANCE)                                 |

| Technology / Process family               | Ultrafast                                         |

| Wafer Testing (EWS) information           |                                                   |

| Electrical testing manufacturing location | ST Tours (FRANCE)                                 |

| Assembly information                      |                                                   |

| Assembly site                             | Subcontractor in CHINA (998G)                     |

| Package description                       | PowerFLAT <sup>™</sup> 5x6                        |

| Molding compound                          | ECOPACK <sup>®</sup> 2 compliant component        |

| Lead finishing/bump solder material       | Pure Tin                                          |

| Final testing information                 |                                                   |

| Testing location                          | Subcontractor in CHINA (998G)                     |

#### 5 TESTS RESULTS SUMMARY

#### 5.1 Test vehicles

| Lot # | Commercial<br>Product | Package                    | Comments                           |

|-------|-----------------------|----------------------------|------------------------------------|

| Lot 1 | FERD20U50DJF-TR       |                            |                                    |

| Lot 2 | FERD30SM100DJF-TR     | PowerFLAT™ 5x6             | Qualification late (EEDD)          |

| Lot 3 | FERD303MI100DJF-IR    | FOWEIFLAT *** 5x6          | Qualification lots (FERD)          |

| Lot 4 | FERD15S50DJF-TR       |                            |                                    |

| Lot 5 | STPS30170DJF-TR       | PowerFLAT <sup>™</sup> 5x6 | Qualification lot (Power Schottky) |

| Lot 6 | STTH8R03DJF-TR        | PowerFLAT <sup>™</sup> 5x6 | Qualification late (Litrafact)     |

| Lot 7 | STTH5R06DJF-TR        | PowerFLAT <sup>™</sup> 5x6 | Qualification lots (Ultrafast)     |

Detailed results in below chapter will refer to these references.

#### 5.2 Test plan and results summary

|             |                                 | <b>A</b> 11/1                                                     | Steps /  | teps / | Failure/SS          |                     |         |         |         |      |      |

|-------------|---------------------------------|-------------------------------------------------------------------|----------|--------|---------------------|---------------------|---------|---------|---------|------|------|

| Test        | Std ref.                        | Conditions                                                        | Duration | SS     | L1                  | L2                  | L3      | L4      | L5      | L6   | L7   |

| Die Oriente | Die Oriented Tests              |                                                                   |          |        |                     |                     |         |         |         |      |      |

| HTRB        | MIL-STD-750-1<br>M1038-Method A | VR = 80V (0.8*VRRM)<br>Tj=110°C (max avoiding<br>thermal runaway) | 1Khrs    | 287    |                     | 0/77                | 0/56    |         | 0/77    |      | 0/77 |

| Package O   | riented Tests                   |                                                                   |          |        |                     |                     |         |         |         |      |      |

| тс          | JESD 22A-104                    | -65/+150°C<br>2cy/h                                               | 500cy    | 461    | 0/77                | 0/77                |         | 0/77    | 0/76    | 0/77 | 0/77 |

| тнв         | JESD22 A-101                    | 85°C; 85% RH<br>VR=80V (0.8*VRRM)                                 | 1Khrs    | 231    |                     | 0/77                |         |         | 0/77    |      | 0/77 |

| UHAST       | JESD22 A-118                    | 130°C 85% RH                                                      | 96hrs    | 231    |                     | 0/77                |         |         | 0/77    |      | 0/77 |

| RSH         | JESD22 B-111<br>(SMD)           | THS 85%RH / 85°C<br>168hrs<br>Sn/Pb dipping 260°C                 | -        | 60     |                     | 0/30 (              | Generic | data)   |         | 0/30 |      |

|             |                                 | Wet ageing<br>SnPb bath 220°C                                     | -        | 10     |                     | 0/10 (Generic data) |         |         |         |      |      |

| SD          | JESD22 B-102                    | Wet ageing<br>SnAgCu bath 245°C                                   | -        | 10     |                     |                     | 0/10 (  | Generic | : data) |      |      |

| 30          | JE2D22 B-102                    | Dry ageing<br>SnPb bath 220°C                                     | -        | 10     | 0/10 (Generic data) |                     |         |         |         |      |      |

|             |                                 | Dryt ageing<br>SnAgCu bath 245°C                                  | -        | 10     | 0/10 (Generic data) |                     |         |         |         |      |      |

| DBT         | DM00112629<br>(ST internal)     | IR reflow<br>after flux deposition                                | -        | 30     | 0/30                |                     |         |         |         |      |      |

Note: Package-oriented tests (except RSH, SD and DBT) are submitted to preconditioning (PC) before test.

## <u>6</u> <u>ANNEXES</u>

# 6.1 **Tests description**

| Test name                                              | Description                                                                                                                                                                        | Purpose                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        | Die Oriented                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>HTRB</b><br>High<br>Temperature<br>Reverse Bias     | The diode is biased in static reverse mode at targeted junction temperature.                                                                                                       | To determine the effects of bias conditions and<br>temperature on solid state devices over time. It<br>simulates the devices' operating condition in an<br>accelerated way. To maximize the electrical field<br>across either reverse-biased junctions or dielectric<br>layers, in order to investigate the failure modes<br>linked to mobile contamination, oxide ageing,<br>layout sensitivity to surface effects. |

|                                                        | Package Oriented                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>THB</b><br>Temperature<br>Humidity Bias             | The device is biased in static configuration<br>minimizing its internal power dissipation, and<br>stored at controlled conditions of ambient<br>temperature and relative humidity. | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                                                                                                             |

| <b>TC</b><br>Temperature Cycling                       | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                      | To investigate failure modes related to the<br>thermo-mechanical stress induced by the different<br>thermal expansion of the materials interacting in<br>the die-package system. Typical failure modes are<br>linked to metal displacement, dielectric cracking,<br>molding compound delamination, wire-bonds<br>failure, die-attach layer degradation.                                                              |

| UHAST<br>Unbiased Highly<br>Accelerated Stress<br>Test | The device is stored in saturated steam, at fixed<br>and controlled conditions of pressure and<br>temperature.                                                                     | To investigate corrosion phenomena affecting die<br>or package materials, related to chemical<br>contamination and package hermeticity.                                                                                                                                                                                                                                                                              |

| <b>RSH</b><br>Resistance to Solder<br>Heat             | Package is dipped by the leads in a solder bath<br>after initial wet ageing (for SMDs only).<br>Assessment by electrical test + no external<br>crack                               | To simulate wave soldering process and verify that package will not be thermally damaged during this step.                                                                                                                                                                                                                                                                                                           |

| <b>SD</b><br>Solderability                             | Ageing + dipping in a solder bath.<br>Assessment by visual inspection of the leads.                                                                                                | To ensure good wettability of the leads                                                                                                                                                                                                                                                                                                                                                                              |

| DBT<br>Dead Bug Test                                   | Leads are covered with soldering flux and are<br>submitted to IR reflow. Assessment by visual<br>inspection of the leads                                                           | To ensure good wettability of the leads                                                                                                                                                                                                                                                                                                                                                                              |

# Reliability Evaluation Report Qualification of PowerFLAT<sup>™</sup> 6x5 at Subcontractor in China

|                     | General Information                                                                                                                                                                                                                                        | L                                 | ocations                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------|

| Product Line        | Rectifiers                                                                                                                                                                                                                                                 | Wafer fab                         | ST CATANIA – ITALY<br>ST SINGAPORE                  |

| Product Description | Field Effect, Power Schottky and<br>Ultrafast Rectifiers                                                                                                                                                                                                   |                                   |                                                     |

| Product perimeter   | FERD15S50DFJ-TR, FERD20U50DJF-TR<br>FERD30M100DJF-TR, STPS3045DJF-TR<br>STPS30M100DJF-TR, STPS30120DJF-TR<br>STPS30170DJF-TR, STPS15L30CDJFTR,<br>STPS30H100DJF-TR, STPS30L30DJF-TR,<br>STPS30M60DJF-TR, STTH30R02DJF-TR<br>STTH5R06DJF-TR, STTH8R03DJF-TR | Assembly plant<br>Reliability Lab | SUBCONTRACTOR –CHINA<br>(998G)<br>ST TOURS - FRANCE |

| Product Group       | ADG                                                                                                                                                                                                                                                        |                                   |                                                     |

| Product division    | Discrete and Filter Division                                                                                                                                                                                                                               |                                   |                                                     |

| Package             | PowerFLAT <sup>™</sup> 5x6                                                                                                                                                                                                                                 | Reliability assessment            | Pass                                                |

| Maturity level step | Qualified                                                                                                                                                                                                                                                  |                                   |                                                     |

#### **DOCUMENT INFORMATION**

| Version | Date         | Pages | Prepared by     | Approved by       | Comments                                                                                                                                                                                           |

|---------|--------------|-------|-----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 04-Dec-2018  | 7     |                 | Julien MICHELON – | FERDxxx qualification:<br>FERD15S50DFJ-TR / FERD20U50DJF-TR<br>FERD30M100DJF-TR                                                                                                                    |

| 2.0     | 29-Jan-2019  |       | Isabelle BALLON |                   | Power Schottky qualification:<br>STPS3045DJF-TR / STPS30M100DJF-TR<br>STPS30120DJF-TR / STPS30170DJF-TR                                                                                            |

| 3.0     | 07-Sept-2022 | 7     | Christophe GOIN |                   | Additional Power Schottky and Ultrafast rectifiers<br>qualification: STPS30H100DJF-TR<br>STPS30L30DJF-TR / STPS30M60DJF-TR<br>STPS15L30CDJFTR / STTH30R02DJF-TR<br>STTH5R06DJF-TR / STTH8R03DJF-TR |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

#### TABLE OF CONTENTS

| 1 |       | CABLE AND REFERENCE DOCUMENTS | - |

|---|-------|-------------------------------|---|

|   |       | BILITY EVALUATION OVERVIEW    | - |

| 3 | 3 1   | OBJECTIVES                    |   |

|   | 3.2   | CONCLUSION                    |   |

| 4 |       |                               |   |

| • | 4.1   | Device description.           |   |

|   | 4.2   | CONSTRUCTION NOTE             | 5 |

| 5 | TESTS | RESULTS SUMMARY               | 6 |

|   | 5.1   | TEST VEHICLE                  | 6 |

|   | 5.2   | TEST PLAN AND RESULTS SUMMARY |   |

| 6 | ANNE  | XES                           |   |

|   | 6.1   | TESTS DESCRIPTION             | 7 |

### **<u>1</u>** APPLICABLE AND REFERENCE DOCUMENTS

| Document reference Short description                                              |                                                         |

|-----------------------------------------------------------------------------------|---------------------------------------------------------|

| JESD 47                                                                           | Stress-Test-Driven Qualification of Integrated Circuits |

| JESD 94 Application specific qualification using knowledge based test methodology |                                                         |

| JESD 22                                                                           | Reliability test methods for packaged devices           |

## 2 GLOSSARY

| SS    | Sample Size                             |

|-------|-----------------------------------------|

| HTRB  | High Temperature Reverse Bias           |

| тнв   | Temperature Humidity Bias               |

| тс    | Temperature Cycling                     |

| UHAST | Unbiased Highly Accelerated Stress Test |

| RSH   | Resistance to Soldering Heat            |

| SD    | Solderability                           |

| DBT   | Dead Bug Test                           |

| GD    | Generic Data                            |

| PC    | Pre-conditioning (before test)          |

#### **<u>3</u>** RELIABILITY EVALUATION OVERVIEW

#### 3.1 **Objectives**

The objective of this report is to qualify PowerFLAT<sup>™</sup> 5x6 at subcontractor in China (998G).

The involved products are listed in table here below:

| Commercial Product |

|--------------------|

| FERD15S50DFJ-TR    |

| FERD20U50DJF-TR    |

| FERD30M100DJF-TR   |

| STPS3045DJF-TR     |

| STPS30M100DJF-TR   |

| STPS30120DJF-TR    |

| STPS30170DJF-TR    |

| STPS15L30CDJFTR    |

| STPS30H100DJF-TR   |

| STPS30L30DJF-TR    |

| STPS30M60DJF-TR    |

| STTH30R02DJF-TR    |

| STTH5R06DJF-TR     |

| STTH8R03DJF-TR     |

The reliability test methodology used follows the JESD47-H: « Stress Test Driven Qualification Methodology ». The following reliability tests ensuing are:

- TC to ensure the mechanical robustness of the products.

- HTRB to evaluate the risk of contamination from the resin and the assembly process versus the die layout sensitivity.

- THB, UHAST to check the robustness to corrosion and the good package hermeticity.

- RSH, Solderability and DBT to check compatibility of package with customer assembly.

#### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. Reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the robustness of the products and safe operation, which is consequently expected during their lifetime.

### **<u>4</u> DEVICE CHARACTERISTICS**

#### 4.1 **Device description**

Refer to products datasheets.

### 4.2 Construction Note

|                                           | FERD15S50DJF / FERD20U50DJF / FERD30SM100DJF |  |  |  |  |

|-------------------------------------------|----------------------------------------------|--|--|--|--|

| Wafer/Die fab. information                |                                              |  |  |  |  |

| Wafer fab manufacturing location          | ST Catania (ITALY)                           |  |  |  |  |

| Technology / Process family               | Field Effect Rectifier                       |  |  |  |  |

| Wafer Testing (EWS) information           |                                              |  |  |  |  |

| Electrical testing manufacturing location | ST SINGAPORE                                 |  |  |  |  |

| Assembly information                      |                                              |  |  |  |  |

| Assembly site                             | Subcontractor in CHINA (998G)                |  |  |  |  |

| Package description                       | PowerFLAT <sup>™</sup> 5x6                   |  |  |  |  |

| Molding compound                          | ECOPACK <sup>®</sup> 2 compliant component   |  |  |  |  |

| Lead finishing/bump solder material       | Pure Tin                                     |  |  |  |  |

| Final testing information                 |                                              |  |  |  |  |

| Testing location                          | Subcontractor in CHINA (998G)                |  |  |  |  |

|                                           | STPS3045DJF-TR / STPS30M100DJF-TR / STPS30120DJF-TR / STPS30170DJF-TR  |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

|                                           | STPS15L30CDJFTR / STPS30H100DJF-TR / STPS30L30DJF-TR / STPS30M60DJF-TR |  |  |  |  |

| Wafer/Die fab. information                |                                                                        |  |  |  |  |

| Wafer fab manufacturing location          | ST SINGAPORE                                                           |  |  |  |  |

| Technology / Process family               | Power Schottky                                                         |  |  |  |  |

| Wafer Testing (EWS) information           |                                                                        |  |  |  |  |

| Electrical testing manufacturing location | ST SINGAPORE                                                           |  |  |  |  |

| Assembly information                      |                                                                        |  |  |  |  |

| Assembly site                             | Subcontractor in CHINA (998G)                                          |  |  |  |  |

| Package description                       | PowerFLAT <sup>™</sup> 5x6                                             |  |  |  |  |

| Molding compound                          | ECOPACK <sup>®</sup> 2 compliant component                             |  |  |  |  |

| Lead finishing/bump solder material       | Pure Tin                                                               |  |  |  |  |

| Final testing information                 |                                                                        |  |  |  |  |

| Testing location                          | Subcontractor in CHINA (998G)                                          |  |  |  |  |

|                                           | STTH30R02DJF-TR / STTH5R06DJF-TR / STTH8R03DJF-TR |  |  |  |  |

|-------------------------------------------|---------------------------------------------------|--|--|--|--|

| Wafer/Die fab. information                |                                                   |  |  |  |  |

| Wafer fab manufacturing location          | ST Tours (FRANCE)                                 |  |  |  |  |

| Technology / Process family               | Ultrafast                                         |  |  |  |  |

| Wafer Testing (EWS) information           |                                                   |  |  |  |  |

| Electrical testing manufacturing location | ST Tours (FRANCE)                                 |  |  |  |  |

| Assembly information                      |                                                   |  |  |  |  |

| Assembly site                             | Subcontractor in CHINA (998G)                     |  |  |  |  |

| Package description                       | PowerFLAT <sup>™</sup> 5x6                        |  |  |  |  |

| Molding compound                          | ECOPACK <sup>®</sup> 2 compliant component        |  |  |  |  |

| Lead finishing/bump solder material       | Pure Tin                                          |  |  |  |  |

| Final testing information                 |                                                   |  |  |  |  |

| Testing location                          | Subcontractor in CHINA (998G)                     |  |  |  |  |

#### 5 TESTS RESULTS SUMMARY

#### 5.1 Test vehicles

| Lot # | Commercial<br>Product | Package                    | Comments                           |  |  |  |

|-------|-----------------------|----------------------------|------------------------------------|--|--|--|

| Lot 1 | FERD20U50DJF-TR       |                            |                                    |  |  |  |

| Lot 2 |                       |                            | Qualification late (EEDD)          |  |  |  |

| Lot 3 | FERD30SM100DJF-TR     | PowerFLAT™ 5x6             | Qualification lots (FERD)          |  |  |  |

| Lot 4 | FERD15S50DJF-TR       |                            |                                    |  |  |  |

| Lot 5 | STPS30170DJF-TR       | PowerFLAT <sup>™</sup> 5x6 | Qualification lot (Power Schottky) |  |  |  |

| Lot 6 | STTH8R03DJF-TR        | PowerFLAT <sup>™</sup> 5x6 | Qualification late (I litrafact)   |  |  |  |

| Lot 7 | STTH5R06DJF-TR        | PowerFLAT <sup>™</sup> 5x6 | Qualification lots (Ultrafast)     |  |  |  |

Detailed results in below chapter will refer to these references.

#### 5.2 Test plan and results summary

| Test        | Ctd rof                         | Conditions                                                        | Steps /  | SS  |                         | Failure/SS |      |      |      |      |      |  |

|-------------|---------------------------------|-------------------------------------------------------------------|----------|-----|-------------------------|------------|------|------|------|------|------|--|

| Test        | Std ref.                        | Conditions                                                        | Duration | 55  | L1                      | L2         | L3   | L4   | L5   | L6   | L7   |  |

| Die Oriente | Die Oriented Tests              |                                                                   |          |     |                         |            |      |      |      |      |      |  |

| HTRB        | MIL-STD-750-1<br>M1038-Method A | VR = 80V (0.8*VRRM)<br>Tj=110°C (max avoiding<br>thermal runaway) | 1Khrs    | 287 |                         | 0/77       | 0/56 |      | 0/77 |      | 0/77 |  |

| Package O   | riented Tests                   |                                                                   |          |     |                         |            |      |      |      |      |      |  |

| тс          | JESD 22A-104                    | -65/+150°C<br>2cy/h                                               | 500cy    | 461 | 0/77                    | 0/77       |      | 0/77 | 0/76 | 0/77 | 0/77 |  |

| тнв         | JESD22 A-101                    | 85°C; 85% RH<br>VR=80V (0.8*VRRM)                                 | 1Khrs    | 231 |                         | 0/77       |      |      | 0/77 |      | 0/77 |  |

| UHAST       | JESD22 A-118                    | 130°C 85% RH                                                      | 96hrs    | 231 |                         | 0/77       |      |      | 0/77 |      | 0/77 |  |

| RSH         | JESD22 B-111<br>(SMD)           | THS 85%RH / 85°C<br>168hrs<br>Sn/Pb dipping 260°C                 | -        | 60  | 0/30 (Generic data) 0/3 |            |      | 0/30 |      |      |      |  |

|             |                                 | Wet ageing<br>SnPb bath 220°C                                     | -        | 10  | 0/10 (Generic data)     |            |      |      |      |      |      |  |

| SD          | JESD22 B-102                    | Wet ageing<br>SnAgCu bath 245°C                                   | -        | 10  | 0/10 (Generic data)     |            |      |      |      |      |      |  |

| 30          | SD JESD22 B-102                 | Dry ageing<br>SnPb bath 220°C                                     | -        | 10  | 0/10 (Generic data)     |            |      |      |      |      |      |  |

|             |                                 | Dryt ageing<br>SnAgCu bath 245°C                                  | -        | 10  | 0/10 (Generic data)     |            |      |      |      |      |      |  |

| DBT         | DM00112629<br>(ST internal)     | IR reflow<br>after flux deposition                                | -        | 30  | 0/30                    |            |      |      |      |      |      |  |

Note: Package-oriented tests (except RSH, SD and DBT) are submitted to preconditioning (PC) before test.

## <u>6</u> <u>ANNEXES</u>

# 6.1 **Tests description**

| Test name                                              | Description                                                                                                                                                                        | Purpose                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Die Oriented                                           |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| <b>HTRB</b><br>High<br>Temperature<br>Reverse Bias     | The diode is biased in static reverse mode at targeted junction temperature.                                                                                                       | To determine the effects of bias conditions and<br>temperature on solid state devices over time. It<br>simulates the devices' operating condition in an<br>accelerated way. To maximize the electrical field<br>across either reverse-biased junctions or dielectric<br>layers, in order to investigate the failure modes<br>linked to mobile contamination, oxide ageing,<br>layout sensitivity to surface effects. |  |  |  |  |  |

|                                                        | Package Oriented                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| <b>THB</b><br>Temperature<br>Humidity Bias             | The device is biased in static configuration<br>minimizing its internal power dissipation, and<br>stored at controlled conditions of ambient<br>temperature and relative humidity. | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| <b>TC</b><br>Temperature Cycling                       | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                      | To investigate failure modes related to the<br>thermo-mechanical stress induced by the different<br>thermal expansion of the materials interacting in<br>the die-package system. Typical failure modes are<br>linked to metal displacement, dielectric cracking,<br>molding compound delamination, wire-bonds<br>failure, die-attach layer degradation.                                                              |  |  |  |  |  |

| UHAST<br>Unbiased Highly<br>Accelerated Stress<br>Test | The device is stored in saturated steam, at fixed<br>and controlled conditions of pressure and<br>temperature.                                                                     | To investigate corrosion phenomena affecting die<br>or package materials, related to chemical<br>contamination and package hermeticity.                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| <b>RSH</b><br>Resistance to Solder<br>Heat             | Package is dipped by the leads in a solder bath<br>after initial wet ageing (for SMDs only).<br>Assessment by electrical test + no external<br>crack                               | To simulate wave soldering process and verify that package will not be thermally damaged during this step.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| <b>SD</b><br>Solderability                             | Ageing + dipping in a solder bath.<br>Assessment by visual inspection of the leads.                                                                                                | To ensure good wettability of the leads                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| DBT<br>Dead Bug Test                                   | Leads are covered with soldering flux and are<br>submitted to IR reflow. Assessment by visual<br>inspection of the leads                                                           | To ensure good wettability of the leads                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |